串口

例如,UART协议可用于发送和接收RS232/RS485帧。

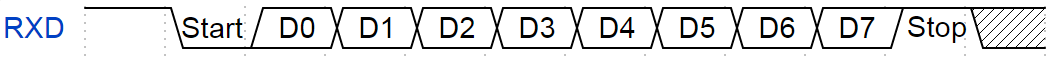

有一个8位帧的示例,无奇偶校验和一位停止位:

总线定义

case class Uart() extends Bundle with IMasterSlave {

val txd = Bool() // Used to emit frames

val rxd = Bool() // Used to receive frames

override def asMaster(): Unit = {

out(txd)

in(rxd)

}

}

UartCtrl

库中实现了Uart控制器。该控制器的特性是使用一个采样窗口读取 rxd 引脚,然后使用多数投票制来过滤其值。

IO名称 |

方向 |

类型 |

描述 |

|---|---|---|---|

config |

in |

UartCtrlConfig |

用于设置控制器的时钟分频器/奇偶校验/停止/数据长度 |

write |

slave |

Stream[Bits] |

用于请求帧传输的反压流端口 |

read |

master |

Flow[Bits] |

用于接收解码帧的流端口 |

uart |

master |

Uart |

与实际实现的连接接口 |

控制器可以通过一个 UartCtrlGenerics 配置对象来实例化:

属性 |

类型 |

描述 |

|---|---|---|

dataWidthMax |

Int |

帧内最大位数 |

clockDividerWidth |

Int |

内部时钟分频器的位宽 |

preSamplingSize |

Int |

指定在一个UART波特开始时丢弃多少samplingTick |

samplingSize |

Int |

指定有多少samplingTick用于采样UART波特中段的 |

postSamplingSize |

Int |

指定在UART波特结束时丢弃多少个samplingTick |