Backend¶

Commit¶

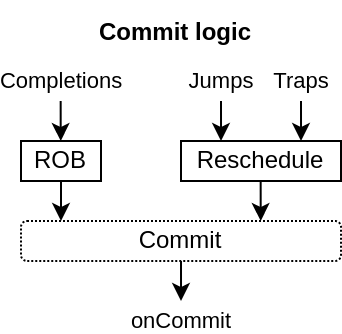

The commit logic is mostly composed :

Reschedule status Which specifies the older ROB ID on which a jump / trap is pending.

Commit Logic Which waits for the older instruction completion before committing it, and eventually applying some reschedule.

Register file¶

The default register file is the dual-port based one

Dual-port based¶

This configuration fit well on FPGA.

Each write port will create its own bank

Each read port will read each bank, and mux the correct one using a distributed-ram-xor-based LVT (live value table)

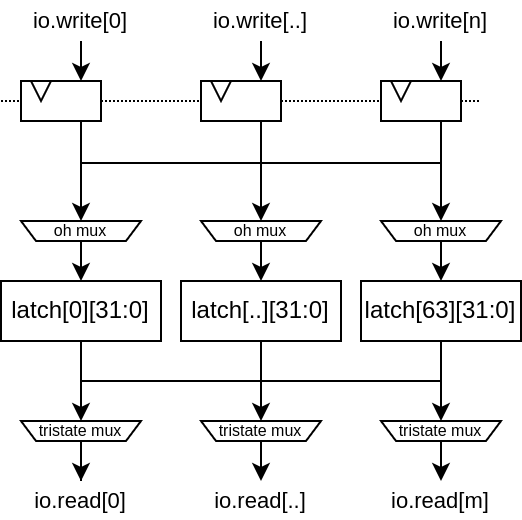

Latch based¶

This configuration fit well on ASIC. It’s implementation was inspired from ibex, with the addition of multi write ports support.

The storage is done via simple latches

The read ports are implemented using tristate “muxes”