关于 SpinalHDL

什么是SpinalHDL?

SpinalHDL 是一种开源高级硬件描述语言及其相关工具。它的开发始于 2014 年 12 月。

SpinalHDL 通过对数字硬件命名和建模使得高效地描述硬件成为可能;最明显的例子是 Reg 和 Latch。在VHDL和Verilog等事件驱动语言中,要使用这两个常见元素,用户必须用过程来模拟它们,以便综合工具可以推断出它是什么单元。使用 SpinalHDL,您只需声明一个 Reg 或 Latch。

SpinalHDL 是一种基于通用语言 Scala 的 领域专用语言 。它带来了几个好处:

有免费的集成开发环境支持它,提供了许多简单文本编辑器所没有的功能:

语法和类型错误在代码中高亮显示

正确的重命名,甚至是跨文件的

智能自动完成/建议

导航工具(转到定义、显示所有引用等)

它允许实现简单到复杂的硬件生成器(元硬件描述),而无需处理多种语言(译者注:例如Python+Verilog)。

备注

Scala 是一种使用 Java 虚拟机 (JVM) 的静态类型、函数式和面向对象的语言。

SpinalHDL 不是什么

SpinalHDL 不是 HLS 工具:它的目标不是自动将抽象算法转换为数字电路。它的目的是借助命名事物来创建新的高层次抽象,以帮助设计人员重用他们的代码,而不是一遍又一遍地编写相同的事物。

SpinalHDL 不是模拟电路建模语言。 VHDL 和 Verilog 使模拟电路设计人员能够向数字设计人员提供其 IP 模型。 SpinalHDL 不解决这种情况,而是供数字设计师描述他们自己的数字设计。

Spinal开发流程

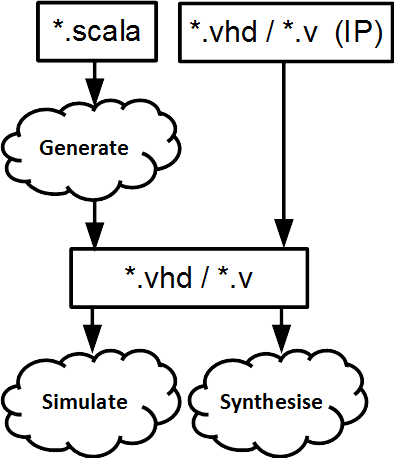

一旦用 SpinalHDL 编写代码,该工具就可以:

生成 VHDL、Verilog 或 SystemVerilog,以这些语言之一实例化它或将其提供给任何仿真器或综合工具。没有逻辑开销,保留层次结构和名称,并且在生成期间运行设计检查。

使用 Verilator 或其他支持的仿真器进行仿真。

由于 SpinalHDL 可以与 VHDL 和(System)Verilog 互操作,因此您既可以用这些语言实例化 SpinalHDL IP(使用生成的代码),也可以用 SpinalHDL 实例化这些语言的 IP(使用 BlackBox)。

备注

SpinalHDL 与基于标准 VHDL/Verilog 的 EDA 工具(仿真器和综合器)*完全可互操作*,因为工具链生成的输出是 VHDL 或 Verilog。

SpinalHDL 相对于 VHDL / Verilog 的优势

由于 SpinalHDL 基于高级语言,因此它提供了多种优势来改进您的硬件编码:

不再需要无休止的布线 - 一行代码完成复杂总线(例如 AXI)的创建和连接。

不断发展的功能 - 创建您自己的总线定义和抽象层。

减少代码大小 - 大幅减少,特别是对于接线而言。这使您能够更好地了解代码库、提高工作效率并减少麻烦。

免费且用户友好的 IDE - 得益于 Scala 工具的自动完成、错误突出显示、导航快捷方式等。

功能强大且简单的类型转换 - 任何数据类型和位向量之间的双向转换。从 CPU 接口加载复杂的数据结构时非常有用。

设计检查 - 早期阶段检查是否存在组合循环/锁存器。

时钟域安全 - 早期 lint 通知是否存在无意识引入的违例跨时钟域信号。

通用设计 - 使用 Scala 构造,因此对硬件描述的通用性没有任何限制。